El Flip Flop Tipo D: El Guardián Sincronizado de los Datos Digitales

El mundo de los dispositivos de almacenamiento digital está poblado por una variedad de componentes, cada uno con su función y características únicas. Entre ellos, el Flip Flop Tipo D se erige como un pilar fundamental, encontrando una aplicación extensiva gracias a su diseño y funcionalidad distintivos. Su nombre, derivado de la "Data" (Datos) que almacena, es un reflejo directo de su propósito principal: actuar como un guardián de la información digital.

En su esencia, un Flip Flop Tipo D es un dispositivo de almacenamiento de un solo bit, capaz de retener un valor binario (0 o 1). Su arquitectura se distingue por tener una única entrada de datos, designada como entrada "D", además de la crucial señal de reloj. La salida de este dispositivo, etiquetada como "Q", es una representación fiel de los datos de entrada, pero con un retraso inherente de un ciclo de reloj, lo que le confiere el apelativo de "flip flop con retardo". Esta propiedad de retraso es lo que lo hace tan valioso en el diseño de sistemas digitales complejos.

La Mecánica del Almacenamiento y la Liberación de Datos

Para comprender la operación de los Flip Flops Tipo D, podemos recurrir a la analogía de un mecanismo de canalización. En este modelo, el resultado de una operación se convierte en el punto de partida para la siguiente, asegurando un flujo continuo y ordenado de información. Los Flip Flops Tipo D son esenciales para mantener la estabilidad de los datos mientras se ejecutan otras operaciones. Capturan y almacenan datos temporalmente, liberándolos solo cuando es necesario. En este sentido, actúan como "guardianes" de los datos digitales, permitiendo que otros componentes del sistema operen sin la necesidad de una entrada de datos constante.

Imaginemos un flujo de señales de datos binarios entrando en el sistema. Cuando la señal de reloj experimenta un cambio de estado, típicamente un flanco ascendente, los datos presentes en la entrada "D" son capturados y almacenados en el flip flop. Posteriormente, la salida "Q" adoptará el mismo valor que la entrada "D" en ese instante. Este comportamiento se puede ilustrar con un segmento de código VHDL:

if clk'event(en="1") then -- Si flanco ascendente en clk q <= d;end if;Este fragmento de código VHDL demuestra la asignación de datos a la salida "Q" basándose en la entrada "D" durante un evento de reloj de flanco ascendente. Por ejemplo, si una secuencia de datos de entrada es "1", "0", "1", "1", "0", y la señal de reloj cambia en el momento en que el tercer bit, un "1", está presente en la entrada "D", la salida "Q" del Flip Flop Tipo D conservará y mostrará este "1" hasta que ocurra la siguiente señal de reloj. Estos mecanismos sistemáticos de almacenamiento y recuperación de datos son el corazón de dispositivos omnipresentes como ordenadores, calculadoras y smartphones, subrayando la importancia de los Flip Flops Tipo D en la electrónica digital moderna.

Diversidad en la Familia del Flip Flop Tipo D

Si bien el concepto fundamental del Flip Flop Tipo D es el almacenamiento de un bit de datos por ciclo de reloj, la realidad es que estos componentes existen en diversas variantes, cada una optimizada para funcionalidades específicas. Esta diversidad permite una adaptación precisa a los requisitos de diferentes circuitos y sistemas digitales.

Flip Flop Tipo D Disparado por Nivel (Latch)

También conocido como "latch", este tipo de flip flop responde al nivel de la señal de reloj. La entrada "D" se transfiere a la salida "Q" mientras la señal de reloj se mantenga en un estado "alto". Una vez que la señal de reloj desciende a un nivel "bajo", la salida "Q" retiene el último valor que tuvo la entrada "D".

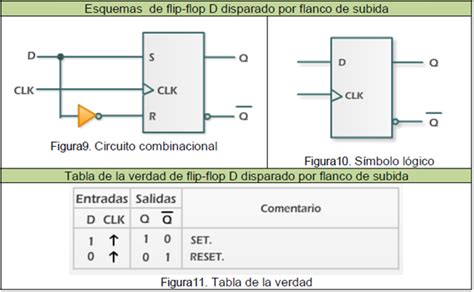

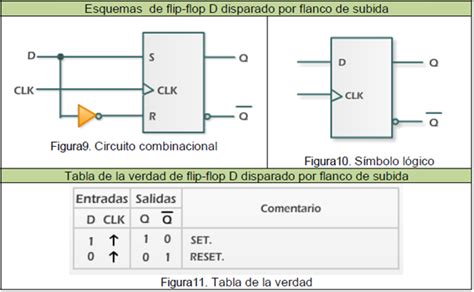

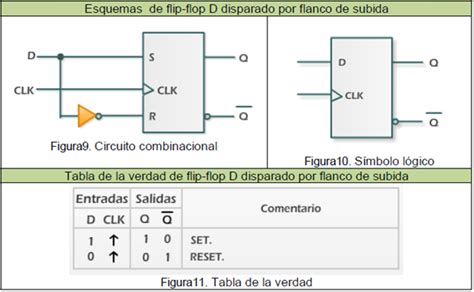

Flip Flop Tipo D Disparado por Flanco Positivo

Este tipo de flip flop es notablemente más sensible. Solo reacciona al flanco ascendente, o flanco positivo, del ciclo de reloj. Esto significa que captura los datos presentes en la entrada "D" únicamente en el instante preciso en que la señal de reloj transita de un estado bajo a uno alto. Durante cualquier otro momento, la salida mantiene su estado anterior.

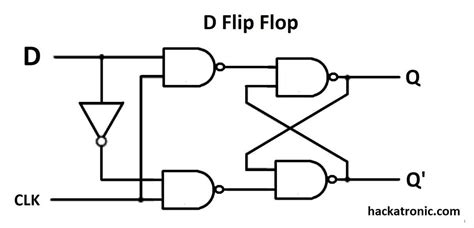

En el núcleo de este funcionamiento se encuentra el concepto de un "flip flop SR con reloj". Mediante la adición de dos compuertas NAND adicionales al flip flop SR básico, se logra la funcionalidad de un flip flop D disparado por flanco positivo. Estas compuertas extra aseguran que el flip flop SR solo esté activo durante la transición de flanco ascendente de la señal de reloj.

El símbolo esquemático para un flip flop D disparado por flanco positivo ilustra claramente sus entradas (D, CLK) y sus salidas (Q, Q'). Durante el flanco ascendente del reloj, si la entrada "D" es "1", la salida "Q" se establecerá en "1" y su complemento "Q'" se convertirá en "0". Esta combinación de la estabilidad de los latches con la precisión de la activación por flanco los convierte en componentes ideales para aplicaciones que exigen integridad de datos y una estricta sincronización.

Flip Flop Tipo D Disparado por Flanco Negativo

En contraposición al disparado por flanco positivo, este flip flop responde al flanco descendente, o flanco negativo, del ciclo de reloj. Captura los datos de la entrada "D" durante la transición de un estado alto a uno bajo en la señal de reloj.

La elección entre estos tipos de flip flops depende intrínsecamente de los requisitos específicos del sistema o circuito digital en cuestión. Cada uno se comporta de manera distinta, respondiendo a diferentes estados o transiciones de la señal de reloj.

La Arquitectura Interna: Puertas Lógicas y el Diseño Maestro-Esclavo

La precisión y fiabilidad de los Flip Flops Tipo D radican en su intrincada circuitería y los principios lógicos que rigen su funcionamiento. En el corazón de estos dispositivos se encuentran las puertas lógicas, componentes fundamentales que ejecutan operaciones binarias.

La mayoría de los Flip Flops Tipo D emplean una arquitectura conocida como "maestro-esclavo". Este diseño consta de dos etapas de flip flop:

- Maestro: Esta etapa reacciona al estado de la entrada de datos en el momento en que llega el pulso de reloj.

- Esclavo: Esta etapa reacciona a la salida de la etapa maestra una vez que el pulso de reloj ha finalizado.

Esta estructura maestro-esclavo asegura que el flip flop D cambie de estado únicamente durante la transición de la señal de reloj, en lugar de hacerlo de forma continua. Durante la fase baja del reloj, la etapa esclava toma la entrada de la etapa maestra y genera la salida. Cada operación dentro de un Flip Flop Tipo D es, por tanto, una coreografía de puertas lógicas sincronizadas con precisión, garantizando la integridad y estabilidad de los datos en los sistemas digitales.

El Principio de Disparo por Flanco: Sincronización Precisa

El principio fundamental de funcionamiento de un Flip Flop Tipo D se basa en el cambio sincrónico de datos. Estos flip flops operan en sincronía con la señal de reloj. Las entradas o los cambios en las mismas influyen directamente en la salida en el momento del disparo, que está determinado por la señal de reloj. Este es el principio de disparo por flanco: la salida solo cambia de estado en el flanco de un impulso de reloj, y no durante su fase alta o baja.

- Cuando D = 0: En el flanco de activación del impulso de reloj, la salida "Q" se restablece a "0" y "Q'" se convierte en "1".

- Cuando D = 1: En el flanco de activación del impulso de reloj, la salida "Q" se establece en "1" y "Q'" se convierte en "0".

Este principio de disparo por flanco es lo que permite a los Flip Flops Tipo D proporcionar un almacenamiento de datos preciso y temporalmente sincronizado. Actúan como espejos que reflejan el estado de la entrada de datos en el flanco exacto del impulso de reloj, almacenando así la información durante el ciclo de reloj.

Diseño Práctico: Construyendo un Flip Flop Tipo D

La comprensión teórica de los Flip Flops Tipo D se enriquece enormemente al adentrarse en su diseño práctico. Construir un Flip Flop Tipo D puede ser una experiencia educativa que consolida el conocimiento sobre estos dispositivos. El diseño se basa en principios de lógica binaria y requiere una comprensión de las compuertas lógicas.

Pasos para el Diseño Básico:

- Componentes Iniciales: Se necesitan cuatro compuertas NAND para construir un Flip Flop Tipo D básico.

- Configuración SR: Las entradas de las dos primeras compuertas NAND se conectan para que funcionen como un flip flop SR. La salida de cada compuerta NAND se dirige a la segunda entrada de la otra.

- La Entrada "D": Una tercera compuerta NAND se conecta a la entrada de "Set" (Establecer). Esto activa el flip flop SR y forma la parte "D" del flip flop Tipo D.

- La Señal de Reloj: Para controlar cuándo se lee la entrada, se introduce una señal de reloj. Una cuarta compuerta NAND se conecta a las entradas de reloj (CLK) y datos (D).

- Conexión Final: La salida de la compuerta NAND de datos y reloj se conecta a la entrada "S" del latch SR con puerta. Esta conexión completa el Flip Flop Tipo D.

El circuito resultante tendrá una estructura donde la entrada "D" y la señal "CLK" interactúan a través de compuertas NAND para controlar las entradas "S" y "R" de un latch SR, produciendo las salidas "Q" y "Q'".

Es crucial probar el Flip Flop Tipo D con distintas combinaciones de entrada para verificar su correcto funcionamiento. Un flip flop funcional debe exhibir el comportamiento de capturar y almacenar el estado de la entrada "D" en el flanco positivo de la señal de reloj, manteniendo dicho estado durante todo el ciclo de reloj hasta el siguiente flanco positivo.

Flip Flop Tipo D con Preselección (Preset) y Borrado (Clear)

Partiendo del diseño estándar, se puede crear una versión más especializada de un Flip Flop Tipo D que incluya entradas adicionales de Preselección (PRE) y Borrado (CLR). Estas entradas proporcionan un control más directo sobre la salida.

- Añadir Compuertas NAND: Se introducen dos compuertas NAND adicionales en el circuito básico.

- Entrada PRE: Una compuerta NAND se conecta a una nueva entrada PRE y se vincula a la entrada R del circuito original.

- Entrada CLR: La segunda compuerta NAND se conecta a una nueva entrada CLR y se enlaza a la entrada S del circuito D Flip Flop original.

- Gestión de Entradas:

- Si CLR es "0" y PRE es "1", el flip flop se borra, restableciendo la salida Q a "0".

- Si CLR es "1" y PRE es "0", el flip flop se activa, estableciendo la salida Q a "1".

- Si tanto CLR como PRE son "1", el circuito opera como un flip flop D normal, donde Q refleja el estado de la entrada D en el momento del disparo.

- Estado Ilegal: Es importante tener precaución con el estado en el que tanto PRE como CLR son "0". En esta condición, el circuito entra en un estado "no permitido" que puede resultar en una salida impredecible.

Este Flip Flop Tipo D con Preselección y Borrado, además de capturar y almacenar datos, permite configurar o borrar directamente la salida, ofreciendo una mayor versatilidad en el diseño de circuitos digitales.

Análisis del Comportamiento: Tablas de Verdad y Ecuaciones

El análisis detallado del funcionamiento de los Flip Flops Tipo D se puede realizar a través de su tabla de verdad operativa, su comportamiento temporal y su ecuación característica. Estos elementos proporcionan información valiosa sobre cómo operan estos dispositivos.

Tabla de Verdad Operativa

La tabla de verdad de un Flip Flop Tipo D (disparado por flanco positivo) resume su comportamiento:

| CLK | D | Q (siguiente estado) | Q' (siguiente estado) || :--: | :-: | :------------------: | :-------------------: || ↑ | 0 | 0 | 1 || ↑ | 1 | 1 | 0 || 0 | X | Q (estado actual) | Q' (estado actual) || 1 | X | Q (estado actual) | Q' (estado actual) |

En esta tabla, "↑" representa el flanco ascendente de la señal de reloj. La entrada "X" indica "no importa", lo que significa que el estado de la entrada D no afecta la salida cuando no hay un flanco de reloj. Durante el flanco de activación (↑), la salida (Q) refleja directamente el valor de la entrada de datos (D), y (Q') se convierte en el complemento de (Q). Durante el resto del tiempo (cuando (CLK) está en nivel bajo o alto sin transición), la salida permanece inalterada, manteniendo su estado anterior.

Comprender la tabla de verdad es fundamental para descifrar la funcionalidad de todos los dispositivos lógicos digitales, y los Flip Flops Tipo D no son una excepción. La clave para leerla reside en entender que la fila CLK indica cuándo puede ocurrir un cambio en la salida (solo en el flanco ascendente), y la fila D determina cuál será la nueva salida (0 o 1) en función del valor de D en ese preciso instante.

Comportamiento Temporal y Ecuación Característica

El comportamiento temporal de un Flip Flop Tipo D se caracteriza por sus tiempos de establecimiento (setup time) y retención (hold time). El tiempo de establecimiento es el período mínimo durante el cual la entrada D debe ser estable antes del flanco de reloj, y el tiempo de retención es el período mínimo durante el cual la entrada D debe permanecer estable después del flanco de reloj.

La ecuación característica de un Flip Flop Tipo D (disparado por flanco positivo) es:

( Q{n+1} = Dn )

Donde:

- ( Q_{n+1} ) es el estado futuro de la salida (Q).

- ( D_n ) es el estado de la entrada (D) en el momento del disparo (n).

Esta ecuación simple encapsula la funcionalidad principal del flip flop: la salida futura es simplemente el valor de la entrada de datos presente en el momento del disparo del reloj.

La Señal de Reloj (CLK): El Corazón Sincronizador

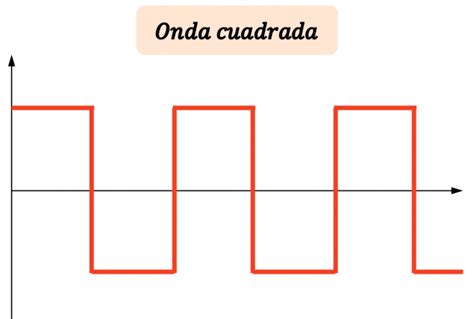

El término "clk", o señal de reloj, es omnipresente en la electrónica digital y las telecomunicaciones. Su función primordial es actuar como un metrónomo, sincronizando las acciones de diversos componentes dentro de un sistema. Esta señal binaria periódica proporciona una referencia de tiempo esencial para las operaciones de temporización, asegurando que los datos se transmitan y procesen a la velocidad correcta.

La señal de reloj, a menudo representada como CLK en esquemas técnicos, suele ser generada por un oscilador dedicado o un circuito especializado. La frecuencia de esta señal determina la velocidad a la que se muestrean, procesan y transmiten los datos. En sistemas de telecomunicaciones complejos, como redes celulares o de satélite, una sincronización precisa es vital para coordinar múltiples dispositivos y garantizar un funcionamiento fluido.

En el contexto de los ordenadores, la frecuencia de reloj, medida en Hercios (Hz), indica el ritmo con el que se procesan los datos. Los procesadores modernos operan a frecuencias que alcanzan miles de millones de Hercios (Gigahertz, GHz). Por ejemplo, una frecuencia de reloj de 1 GHz implica un período de reloj de un nanosegundo. Sin embargo, el rendimiento de un procesador no depende únicamente de su frecuencia de reloj, sino también de su arquitectura, la cantidad de instrucciones por ciclo (IPC) y la eficiencia en el acceso a la memoria.

Aplicaciones Prácticas: Más Allá del Almacenamiento Básico

Los Flip Flops Tipo D son componentes fundamentales que habilitan una amplia gama de funcionalidades en sistemas digitales, incluyendo:

Registradores de Desplazamiento (Shift Registers)

Estos circuitos utilizan Flip Flops Tipo D para desplazar información bit a bit a cada pulso de reloj. Pueden operar en modo de carga serial (los datos se introducen uno tras otro) o en modo de carga paralela (los datos se introducen simultáneamente en todas las entradas). Los registradores de desplazamiento son cruciales para la conversión de datos de formato paralelo a serie y viceversa.

Un ejemplo es el circuito integrado 74165, que contiene un registrador de desplazamiento de 8 bits con entrada paralela y salida serie. Permite la transformación de datos paralelos en un flujo de datos serial, una operación común en muchas aplicaciones digitales.

El concepto de "contador de timbre" (ring counter) también se basa en registradores de desplazamiento. En este circuito, un bit "1" se desplaza secuencialmente a través de las etapas del registro. Cuando el bit "1" alcanza la última etapa, se realimenta a la primera, creando un ciclo continuo.

Contadores

Aunque no todos los contadores utilizan exclusivamente Flip Flops Tipo D, su capacidad para almacenar y actualizar estados de forma sincronizada los hace idóneos para la construcción de diversos tipos de contadores, incluyendo contadores divisores de frecuencia y contadores que operan en módulos de valores impares. En un divisor de frecuencia, por ejemplo, la frecuencia de la señal de reloj se reduce en una proporción determinada por el número de etapas del circuito.

Memorias y Procesamiento de Datos

En su forma más básica, los Flip Flops Tipo D son los bloques de construcción de las memorias RAM estáticas (SRAM). Cada celda de memoria SRAM utiliza un conjunto de flip flops para almacenar un bit de información. Además, en sistemas de procesamiento de datos, los flip flops se utilizan para almacenar resultados intermedios, mantener estados de control y sincronizar operaciones complejas.

La capacidad de los Flip Flops Tipo D para capturar un valor en un momento específico y mantenerlo hasta el siguiente ciclo de reloj es lo que les permite desempeñar un papel tan crucial en la arquitectura de los sistemas digitales modernos, desde los microprocesadores hasta los dispositivos de telecomunicaciones. Son, en esencia, los pilares sobre los cuales se construye la lógica secuencial y el almacenamiento temporal de información digital.

tags: #conexion #circuito #d #clk